| MODEL NO :     | TM034XDZP02                    |

|----------------|--------------------------------|

| MODEL VERSION: | 00                             |

| SPEC VERSION:  | Ver 1.0                        |

| ISSUED DATE:   | 2018-07-13                     |

|                | Specification ct Specification |

Customer :\_\_\_\_\_

| Approved by | Notes |

|-------------|-------|

|             |       |

### **TIANMA Confirmed:**

| Prepared by | Checked by                                     | Approved by |

|-------------|------------------------------------------------|-------------|

| Haiping_luo | Huixuan_chen Chunyang_huang Yujie_ma Jufang_he | Guangkun_an |

This technical specification is subjected to change without notice

# **Table of Contents**

| Tab | ole of Contents                  | 2  |

|-----|----------------------------------|----|

| Red | cord of Revision                 | 3  |

|     | General Specifications           |    |

| 2   | Input/Output Terminals           |    |

|     | Absolute Maximum Ratings         |    |

| 4   | Electrical Characteristics       |    |

| 5   | Timing Chart                     |    |

| 6   | Optical Characteristics          |    |

| 7   | Environmental / Reliability Test | 19 |

| 8   | Mechanical Drawing               | 20 |

| 9   | Packing Drawing                  | 21 |

| 9.1 |                                  | 21 |

| 10  |                                  |    |

## **Record of Revision**

| Rev | Issued Date | Description                       | Editor      |

|-----|-------------|-----------------------------------|-------------|

| 1.0 | 2018-07-13  | Preliminary Specification Release | Haiping_luo |

|     |             |                                   |             |

|     |             |                                   |             |

|     |             |                                   |             |

|     |             |                                   |             |

|     |             |                                   |             |

|     |             |                                   | <b>&gt;</b> |

|     |             |                                   |             |

|     |             |                                   |             |

|     |             |                                   |             |

|     |             |                                   |             |

|     |             |                                   |             |

|     |             |                                   |             |

|     |             |                                   |             |

# 1 General Specifications

|                            | Feature                  | Spec                        |

|----------------------------|--------------------------|-----------------------------|

|                            | Size                     | 3.4 inch                    |

|                            | Resolution               | 800(RGB)×800                |

|                            | Technology Type          | a-Si                        |

| Display Spec.              | Pixel Configuration      | R.G.B. Vertical Stripe      |

| Display opec.              | Pixel pitch(mm)          | 0.1095×0.1095               |

|                            | Display Mode             | SFT                         |

|                            | Surface Treatment        | HC                          |

|                            | Viewing Direction        | All direction               |

|                            | LCM (W x H x D) (mm)     | 96.6(W) x 99.0(H) x 2.45(D) |

| <br>  Mechanical           | LCD Active Area(mm)      | 87.6(W) ×87.6 (H)           |

| Characteristics            | Matching Connection Type | ZIF                         |

|                            | LED Numbers              | 8 white LEDs                |

|                            | Weight (g)               | TBD                         |

|                            | Interface                | MIPI 3-Lane                 |

| Electrical Characteristics | Color Depth              | 16.7M                       |

| Characteristics            | Driver IC                | ILI9881C                    |

Note 1: Viewing direction for best image quality is different from TFT definition. There is a 180 degree shift.

Note 2: Requirements on Environmental Protection: Q/S0002

Note 3: LCM weight tolerance: ± 5%

# 2 Input/Output Terminals

## 2.1 LCM Interface Description

| Pin<br>No. | Symbol   | I/O | Function              | Remark |

|------------|----------|-----|-----------------------|--------|

| 1          | GND      | Р   | Ground                |        |

| 2          | LEDA     | Р   | LED Anode             |        |

| 3          | LEDA     | Р   | LED Anode             |        |

| 4          | LEDK     | Р   | LED Cathode           |        |

| 5          | LEDK     | Р   | LED Cathode           |        |

| 6          | GND      | Р   | Ground                |        |

| 7          | VDD(-5V) | Р   | -5V INPUT             |        |

| 8          | VDD(-5V) | Р   | -5V INPUT             |        |

| 9          | GND      | Р   | Ground                |        |

| 10         | VDD(+5V) | Р   | +5V INPUT             |        |

| 11         | VDD(+5V) | Р   | +5V INPUT             |        |

| 12         | GND      | Р   | Ground                |        |

| 13         | IOVCC    | Р   | Power supply 1.8V     |        |

| 14         | IOVCC    | Р   | Power supply 1.8V     |        |

| 15         | GND      | Р   | Ground                |        |

| 16         | RESET    | I   | Global Reset Pin      |        |

| 17         | GND      | Р   | Ground                |        |

| 18         | TE       | _1  | tearing effect output |        |

| 19         | GND      | Р   | Ground                |        |

| 20         | NC       | 1   | No connect            |        |

| 21         | NC       | 1   | No connect            |        |

| 22         | NC       | 1   | No connect            |        |

| 23         | GND      | Р   | Ground                |        |

| 24         | LAN2_P   | I/O | MIPI lane 2+          |        |

| 25         | NC       | 1   | No connect            |        |

| 26         | LAN2_N   | I/O | MIPI lane 2-          |        |

| 27         | GND      | Р   | Ground                |        |

| 28         | CLK_P    | I/O | MIPI clock +          |        |

#### Model No. TM034XDZP02-00

| NC     | /                                               | No connect                                                                  |                                                                                                                                                                                                   |

|--------|-------------------------------------------------|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK_N  | I/O                                             | IMIPI clock -                                                               |                                                                                                                                                                                                   |

| GND    | Р                                               | Ground                                                                      |                                                                                                                                                                                                   |

| LAN1_P | I/O                                             | MIPI lane 1+                                                                |                                                                                                                                                                                                   |

| NC     | /                                               | No connect                                                                  |                                                                                                                                                                                                   |

| LAN1_N | I/O                                             | MIPI lane 1-                                                                |                                                                                                                                                                                                   |

| GND    | Р                                               | Ground                                                                      |                                                                                                                                                                                                   |

| LAN0_P | I/O                                             | MIPI lane 0+                                                                |                                                                                                                                                                                                   |

| NC     | /                                               | No connect                                                                  |                                                                                                                                                                                                   |

| LAN0_N | I/O                                             | MIPI lane 0-                                                                |                                                                                                                                                                                                   |

| GND    | Р                                               | Ground                                                                      |                                                                                                                                                                                                   |

|        | CLK_N GND LAN1_P NC LAN1_N GND LAN0_P NC LAN0_N | CLK_N I/O GND P LAN1_P I/O NC / LAN1_N I/O GND P LAN0_P I/O NC / LAN0_N I/O | CLK_N I/O IMIPI clock -  GND P Ground  LAN1_P I/O MIPI lane 1+  NC / No connect  LAN1_N I/O MIPI lane 1-  GND P Ground  LAN0_P I/O MIPI lane 0+  NC / No connect  MIPI lane 0+  NC / MIPI lane 0- |

# 3 Absolute Maximum Ratings

### 3.1 LCM absolute maximum reatings

GND=0V

| Item                    | Symbol   | MIN  | MAX        | Unit       | Remark           |

|-------------------------|----------|------|------------|------------|------------------|

| Power Supply Voltage    | IOVCC    | -0.3 | 3.3        | V          |                  |

| Power Supply Voltage    | VDD(+5V) | -0.3 | 6.5        | V          | Note1            |

| Power Supply Voltage    | VDD(-5V) | -6.5 | +0.3       | V          |                  |

| Operating Temperature   | Тор      | -20  | 70         | $^{\circ}$ |                  |

| Storage Temperature     | Tst      | -30  | 80         | $^{\circ}$ |                  |

|                         |          |      | ≪95        | %          | Ta≤40°C          |

| Dolotivo Ukraiditu      |          |      | ≪85        | %          | 40°C < Ta ≤ 50°C |

| Relative Humidity Note2 | RH       |      | ≪55        | %          | 50°C < Ta ≤ 60°C |

| INULEZ                  |          |      | ≪36        | %          | 60°C < Ta ≤ 70°C |

|                         |          |      | ≤24        | %          | 70°C < Ta ≤ 80°C |

| Absolute Humidity       | АН       |      | <b>≤70</b> | g/m³       | Ta>70℃           |

Table 3 Absolute Maximum Ratings

Note1: Input voltage include R0~R5, G0~G5, B0~B5, Dotclk, Hsync, Vsync, Enable, R/L, U/D.

## 4 Electrical Characteristics

### 4.1 LCD electrical characteristics

GND=0V,Ta=25℃

| Item                           |           | Symbol   | MIN       | TYP | MAX       | Unit     | Remark |

|--------------------------------|-----------|----------|-----------|-----|-----------|----------|--------|

| Logic operating voltage        |           | IOVCC    | 1.7       | 1.8 | 1.9       | ٧        |        |

| Positive source output voltage |           | VDD(+5V) | 4.9       | 5   | 5.1       | <b>\</b> |        |

| Negative source output voltage |           | VDD(-5V) | -5.1      | -5  | -4.9      | V        |        |

| Input High Level Signal        |           | VIH      | 0.7*IOVCC | -   | IOVCC     |          |        |

| Voltage Low Level              |           | VIL      | 0         | -   | 0.3*IOVCC | V        |        |

| Output<br>Voltage High Level   |           | Voн      | 0.8 IOVCC | -   | IOVCC     |          |        |

| voitage                        | Low Level | VOL      | 0         | -   | 0.2 IOVCC |          |        |

Table 4.1 LCD module electrical characteristics

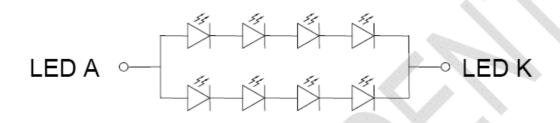

### 4.4 Backlight Unit

Ta=25℃

| Item                | Symbol         | Min | Тур    | Max | Unit | Remark       |

|---------------------|----------------|-----|--------|-----|------|--------------|

| Forward Current     | l <sub>F</sub> | -   | 20     | -   | mA   | For each LED |

| Forward Voltage     | $V_{F}$        | 2.9 | 3.2    | 3.4 | V    | For each LED |

| Operating Life Time | -              | -   | 20,000 | -   | Hrs  | For each LED |

Note1: Figure below shows the connection of backlight LED.

# LED CIRCUIT

(If=40mA / Vf=12.8V TYP)

Note 2: 1LED:  $V_F = 3.2V$   $I_F = 20mA$ Note 3:  $I_F$  is defined for one LED.

Optical performance should be evaluated at Ta=25°C only.

If LED is driven by high current, high ambient temperature & humidity condition. The life time of LED will be reduced. Operating life means brightness goes down to 50% initial brightness. Typical operating life time is estimated data

## 5 Timing Chart

### 5.1 LCM Timing

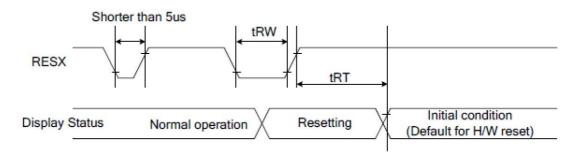

### 5.1.1 Reset timing characteristics

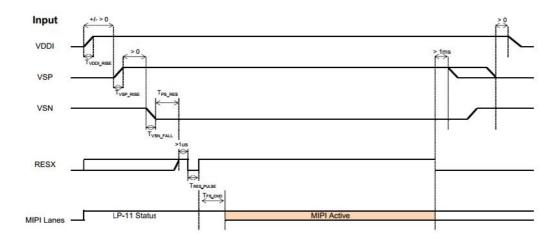

Figure 124: Reset Timing

Table 47: Reset Timing

| Signal | Symbol | Parameter            | Min | Max              | Unit |

|--------|--------|----------------------|-----|------------------|------|

| RESX   | tRW    | Reset pulse duration | 10  |                  | uS   |

|        | +DT    | Deseterant           |     | 5 (note 1,5)     | mS   |

|        | tRT    | Reset cancel         |     | 120 (note 1,6,7) | mS   |

#### Notes:

- The reset cancel also includes required time for loading ID bytes, VCOM setting and other settings from EEPROM to registers. This loading is done every time when there is H/W reset cancel time (tRT) within 5 ms after a rising edge of RESX.

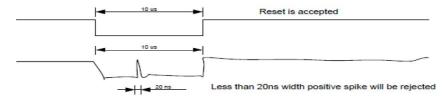

- Spike due to an electrostatic discharge on RESX line does not cause irregular system reset according to the Table 48

Table 48: Reset Descript

| RESX Pulse           | Action         |

|----------------------|----------------|

| Shorter than 5us     | Reset Rejected |

| Longer than 10us     | Reset          |

| Between 5us and 10us | Reset starts   |

- During the Resetting period, the display will be blanked (The display enters the blanking sequence, which maximum time is 120 ms, when Reset Starts in the Sleep Out mode. The display remains the blank state in the Sleep In mode.) and then return to Default condition for Hardware Reset.

- 4. Spike Rejection can also be applied during a valid reset pulse, as shown below:

Figure 125: Positive Noise Pulse during Reset Low

- 5. When Reset applied during Sleep In Mode.

- 6. When Reset applied during Sleep Out Mode.

- It is necessary to wait 5msec after releasing RESX before sending commands. Also Sleep Out command cannot be sent for 120msec.

### 5.1.2 High Speed Mode

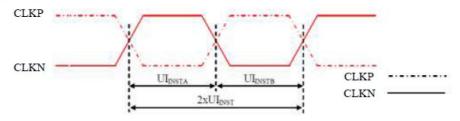

#### 18.4.2. High Speed Mode - Clock Channel Timing

Figure 116: DSI Clock Channel Timing

Table 38: DSI Clock Channel Timing

| Signal | Symbol                                             | Parameter               | Min    | Max  | Unit |

|--------|----------------------------------------------------|-------------------------|--------|------|------|

| CLKP/N | 2xUI <sub>INST</sub>                               | Double UI instantaneous | Note 2 | 25   | ns   |

| CLKP/N | Ul <sub>INSTA</sub> , Ul <sub>INSTB</sub> (Note 1) | UI instantaneous Half   | Note 2 | 12.5 | ns   |

#### Notes:

- 1. UI = UIINSTA = UIINSTB

- 2. Define the minimum value, see Table 39.

Table 39: Limited Clock Channel Speed

| Data type                                                   | Two Lanes speed | Three Lanes<br>speed | Four Lanes<br>speed |

|-------------------------------------------------------------|-----------------|----------------------|---------------------|

| Data Type = 00 1110 (0Eh), RGB 565, 16 UI per Pixel         | 566 Mbps        | 466 Mbps             | 366 Mbps            |

| Data Type = 01 1110 (1Eh), RGB 666, 18 UI per Pixel         | 637 Mbps        | 525 Mbps             | 412 Mbps            |

| Data Type = 10 1110 (2Eh), RGB 666 Loosely, 24 UI per Pixel | 850 Mbps        | 700 Mbps             | 550 Mbps            |

| Data Type = 11 1110 (3Eh), RGB 888, 24 UI per Pixel         | 850 Mbps        | 700 Mbps             | 550 Mbps            |

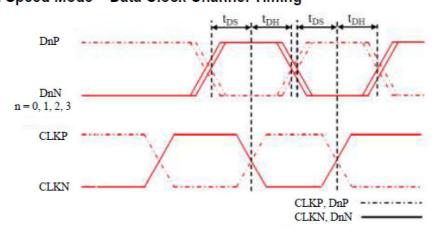

### 18.4.3. High Speed Mode - Data Clock Channel Timing

Figure 117: DSI Data to Clock Channel Timings

Table 40: DSI Data to Clock Channel Timings

| Signal           | Symbol | Parameter                | Min     | Max        |

|------------------|--------|--------------------------|---------|------------|

| D-001 - 0 - 14   | tos    | Data to Clock Setup time | 0.15xUI | -          |

| DnP/N, n=0 and 1 | ton    | Clock to Data Hold Time  | 0.15xUI | <u>171</u> |

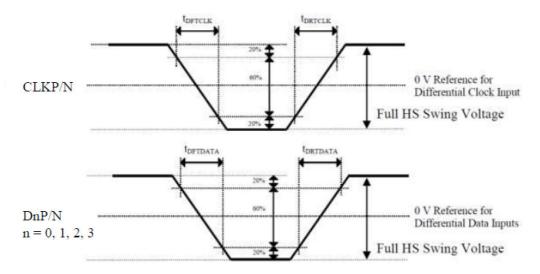

### 18.4.4. High Speed Mode - Rising and Falling Timings

Figure 118: Rising and Falling Timings on Clock and Data Channels

Table 41: Rise and Fall Timings on Clock and Data Channels

| D                                |                            |               | Specification |       |        |

|----------------------------------|----------------------------|---------------|---------------|-------|--------|

| Parameter                        | Symbol                     | Condition     | Min           | Тур   | Max    |

| Differential Disc Time for Cleak |                            | CLEDIN        | 150 po        |       | 0.3UI  |

| Differential Rise Time for Clock | TORTOLK                    | CLKP/N 150 ps | 150 ps        | -     | (Note) |

| Differential Rise Time for Data  |                            | DnP/N         | 150 ps        | 15    | 0.3UI  |

| Differential Rise Time for Data  | TORTDATA                   | n=0 and 1     | 100 ps        |       | (Note) |

| Differential Fall Time for Cleak |                            | 011/04/1 450  |               | 0.3UI |        |

| Differential Fall Time for Clock | t <sub>DFTCLK</sub> CLKP/N | CLKP/N        | 150 ps        |       | (Note) |

| Differential Call Time for Date  | toftdata                   | DnP/N         | 150 po        |       | 0.3UI  |

| Differential Fall Time for Data  |                            | n=0 and 1     | 150 ps        | _     | (Note) |

**Note:** The display module has to meet timing requirements, which are defined for the transmitter (MCU) on MIPI D-Phy standard.

### 5.1.3 Low Speed Mode

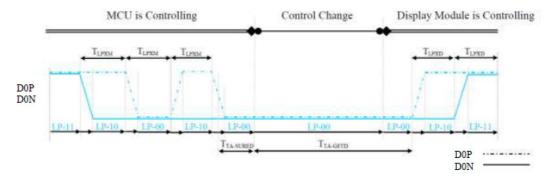

#### 18.4.5. Low Speed Mode - Bus Turn Around

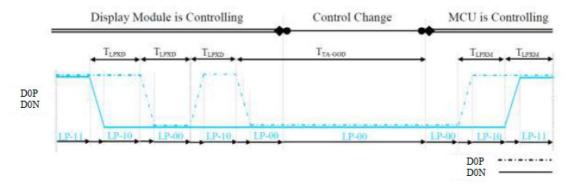

Lower Power Mode and its State Periods on the Bus Turnaround (BTA) from the MCU to the Display Module (ILI9881C) are illustrated for reference purposes below.

Figure 119: BTA from the MCU to the Display Module

Lower Power Mode and its State Periods on the Bus Turnaround (BTA) from the Display Module (ILI9881C) to the MCU are illustrated for reference purposes below.

Figure 120: BTA from the Display Module to the MCU

Unit Signal Symbol Description Min Max Length of LP-00, LP-01, LP-10 or LP-11 periods D0P/N TIPXM 50 75 ns MCU → Display Module (ILI9881C) Length of LP-00, LP-01, LP-10 or LP-11 periods D0P/N TLPXD 50 75 ns Display Module (ILI9881C) → MCU D0P/N Time-out before the Display Module (ILI9881C) starts driving 2xT<sub>LPXD</sub> T<sub>TA-SURED</sub>

Table 42: Low Power State Period Timings - A

Table 43: Low Power State Period Timings - B

| Signal | Symbol               | Description                                        | Time                | Unit |

|--------|----------------------|----------------------------------------------------|---------------------|------|

| D0P/N  | T <sub>TA-GETD</sub> | Time to drive LP-00 by Display Module (ILI9881C)   | 5xT <sub>LPXD</sub> | ns   |

| D0P/N  | T <sub>TA-GOD</sub>  | Time to drive LP-00 after turnaround request - MCU | 4xT <sub>LPXD</sub> | ns   |

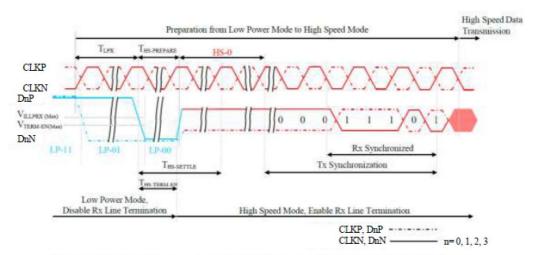

#### 18.4.6. Data Lanes from Low Power Mode to High Speed Mode

Figure 121: Data Lanes - Low Power Mode to High Speed Mode Timings

Table 44: Data Lanes - Low Power Mode to High Speed Mode Timings

| Signal             | Symbol                  | Description                                                                             | Min     | Max     | Unit |

|--------------------|-------------------------|-----------------------------------------------------------------------------------------|---------|---------|------|

| DnP/N, n = 0 and 1 | T <sub>LPX</sub>        | Length of any Low Power State Period                                                    | 50      | -       | ns   |

| DnP/N, n = 0 and 1 | T <sub>HS-PREPARE</sub> | Time to drive LP-00 to prepare for HS Transmission                                      | 40+4xUI | 85+6xUI | ns   |

| DnP/N, n = 0 and 1 | T <sub>HS-TERM-EN</sub> | Time to enable Data Lane Receiver line termination measured from when Dn crosses VILMAX | н       | 35+4xUI | ns   |

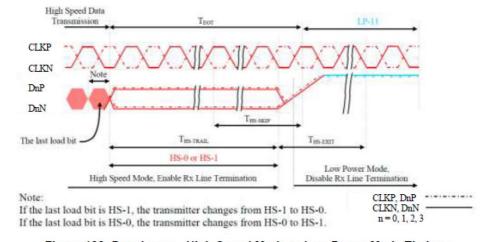

#### 18.4.7. Data Lanes from High Speed Mode to Low Power Mode

Figure 122: Data Lanes - High Speed Mode to Low Power Mode Timings

Table 45: Data Lanes - High Speed Mode to Low Power Mode Timings

| Signal Symbol Description |                      | Description                                                              | Min | Max     | Unit |

|---------------------------|----------------------|--------------------------------------------------------------------------|-----|---------|------|

| DnP/N, n = 0 and 1        | T <sub>HS-SKIP</sub> | Time-Out at Display Module (ILI9881C) to ignore transition period of EoT | 40  | 55+4xUI | ns   |

| DnP/N, n = 0 and 1        | T <sub>HS-EXIT</sub> | Time to driver LP-11 after HS burst                                      | 100 | _       | ns   |

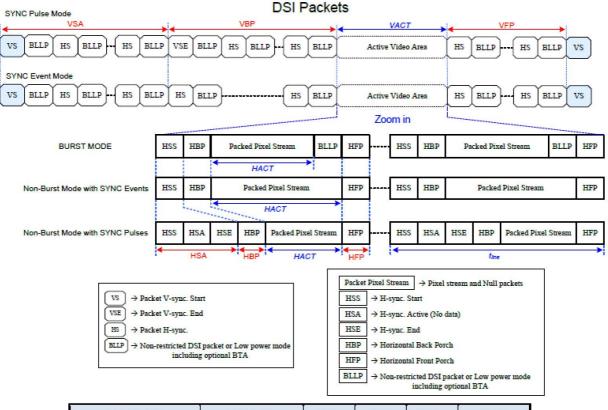

#### 18.4.9. Timing for DSI video mode

| Parameters              | Symbols           | Min.        | Тур. | Max.   | Units     |

|-------------------------|-------------------|-------------|------|--------|-----------|

| Vertical sync. active   | VSA               | 2 (Note 6)  | (1)  | -      | Line      |

| Vertical Back Porch     | VBP               | 14 (Note 6) | -    | -      | Line      |

| Vertical Front Porch    | VFP               | 8 (Note 6)  | -    | -      | Line      |

| Active lines per frame  | VACT              | -           | 1280 | -      | Line      |

| Horizontal sync. active | HSA               | 2           | = 1  | Η.     | Pixel     |

| Horizontal Porch period | HSA + HBP + HFP   | 1.6         | (1)  | -      | us        |

| Active pixels per line  | HACT              | -           | 720  | =      | Pixel     |

| Bit rate                | BR <sub>bps</sub> | 385         |      | Note 5 | Mbps/lane |

1 UI=1/Bit rate

HSA(pixel)= (tHSA\*lane number ) / (UI\* pixel format )

HBP(pixel)= (tHBP\*lane number ) / (UI\* pixel format )

HFP(pixel)= (tHFP\*lane number ) / (UI\* pixel format )

Frame Rate =

$$\frac{BR_{bps} \times Lane_{num}}{(VACT+VSA+VBP+VFP) \times (HACT+HSA+HBP+HFP) \times Pixel Format}$$

Example: BR<sub>bps</sub> = 457Mbps/lane, 1UI=2.1883ns, Frame rate=60Hz, VACT=1280, VSA=2, VBP=30, VFP=20, HACT=720, HSA=33, HBP=100, HFP=100, Lane<sub>num</sub>=4(lane), Pixel Format=24(bit).

# 5.1.4 POWER ON/OFF SEQUENCE

| Symbol                 | Characteristics           | Min. | Тур. | Max. | Units |

|------------------------|---------------------------|------|------|------|-------|

| T <sub>VDDI_RISE</sub> | VDDI Rise time            | 10   | -    | -    | us    |

| T <sub>VSP_RISE</sub>  | VSP Rise time             | 130  | -    | -    | us    |

| T <sub>VSN_FALL</sub>  | VSN Fall time             | 200  | -    | 191  | us    |

| T <sub>PS_RES</sub>    | VDDI/VSP on to Reset high | 5    | -    | -    | ms    |

| T <sub>RES_PULSE</sub> | Reset low pulse time      | 10   | -    | -    | us    |

| T <sub>FS_CMD</sub>    | Reset to first command    | 10   | -    | -    | ms    |

## 6 Optical Characteristics

| Item           |             | Symbol   | Condition    | Min   | Тур   | Max   | Unit              | Remark   |

|----------------|-------------|----------|--------------|-------|-------|-------|-------------------|----------|

|                |             | θТ       |              | 70    | 80    | -     |                   |          |

| Viou Ang       | loo         | θВ       | CR≧10        | 70    | 80    | -     | Dograd            | Note2    |

| view Ang       | View Angles |          | CR≡ IU       | 70    | 80    | -     | Degree            | Notez    |

|                |             | θR       |              | 70    | 80    | -     | 4                 |          |

| Contrast R     | atio        | CR       | θ=0°         | 600   | 800   | -     |                   | Note 3   |

| Chromaticity   | White       | х        | Backlight is | 0.255 | 0.295 | 0.335 |                   | Note 1,5 |

| Cilioniaticity | vviiite     | у        | on           | 0.282 | 0.322 | 0.362 |                   | Note 1,5 |

| Uniformi       | ty          | U        |              | 75    | 80    | -     | %                 | Note 6   |

| Response       | Time        | Ton+Toff | 1            | -     | 25    | 35    |                   | Note 1,4 |

| NTSC           | _           | -        | -            | 65    | 70    | -     | %                 | Note 5   |

| Luminan        | ce          | L        | -            | 300   | 380   | _     | cd/m <sup>2</sup> | Note 7   |

#### **Test Conditions:**

- 1.  $I_F$ = 20 mA(one LED), and the ambient temperature is 25 °C.

- 2. The test systems refer to Note 1 and Note 2.

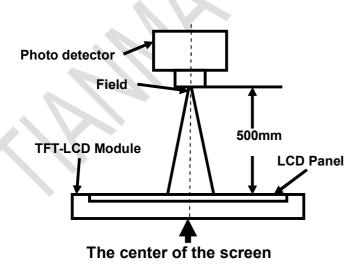

Note 1: Definition of optical measurement system.

The optical characteristics should be measured in dark room. After 5 Minutes operation, the optical properties are measured at the center point of the LCD screen. All input terminals LCD panel must be ground when measuring the center area of the panel.

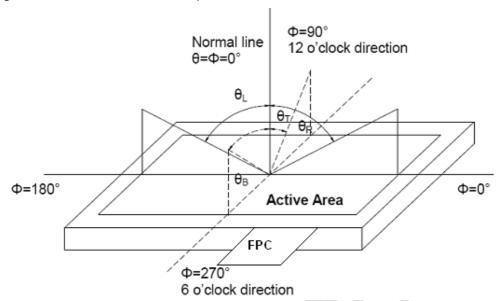

Note 2: Definition of viewing angle range and measurement system.

viewing angle is measured at the center point of the LCD

Note 3: Definition of contrast ratio

Contrast ratio (CR) =  $\frac{\text{Luminance measured when LCD is on the "White" state}}{\text{Luminance measured when LCD is on the "Black" state}}$

"White state ": The state is that the LCD should drive by Vwhite.

"Black state": The state is that the LCD should drive by Vblack.

Vwhite: To be determined Vblack: To be determined.

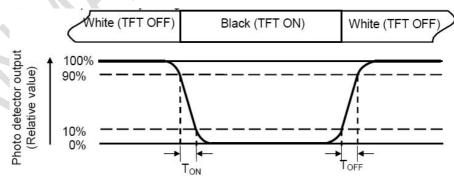

Note 4: Definition of Response time

The response time is defined as the LCD optical switching time interval between "White" state and "Black" state. Rise time  $(T_{ON})$  is the time between photo detector output intensity changed from 90% to 10%. And fall time  $(T_{OFF})$  is the time between photo detector output intensity changed from 10% to 90%.

Note 5: Definition of color chromaticity (CIE1931)

Color coordinates measured at center point of LCD.

Note 6: Definition of Luminance Uniformity

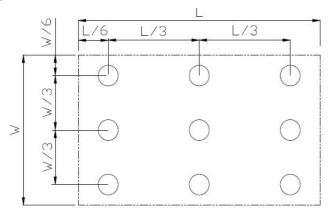

Active area is divided into 9 measuring areas (Refer Fig. 2). Every measuring point is placed at the center of each measuring area.

Luminance Uniformity (U) = Lmin/Lmax

L-----Active area length W----- Active area width

Lmax: The measured Maximum luminance of all measurement position.

Lmin: The measured Minimum luminance of all measurement position.

Note 7: Definition of Luminance: Measure the luminance of white state at center point.

# 7 Environmental / Reliability Test

#### 7.1 LCM+CTP

| No | Test Item                                      | Condition                                                   | Remarks                                                                                                   |

|----|------------------------------------------------|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| 1  | High Temperature Operation                     | Ts=+70℃±2℃, 120hrs                                          | IEC60068-2-1:2007<br>GB2423.2-2008                                                                        |

| 2  | Low Temperature Operation                      | Ta=-20℃±2℃, 120hrs                                          | IEC60068-2-1:2007<br>GB2423.1-2008                                                                        |

| 3  | High Temperature Storage                       | Ta=+80℃±2℃, 120hrs                                          | IEC60068-2-1:2007<br>GB2423.2-2008                                                                        |

| 4  | Low Temperature<br>Storage                     | Ta=-30℃±2℃, 120hrs                                          | IEC60068-2-1:2007<br>GB2423.1-2008                                                                        |

| 5  | Storage at High<br>Temperature and<br>Humidity | Ta=+60℃, 90% RH, 120hrs                                     | IEC60068-2-78 :2001<br>GB/T2423.3—2006                                                                    |

| 6  | Thermal Shock (non-operation)                  | (-30°C/30min~80°C/30min)*20 cycles<br>Change Speed: 8°C/min | Start with cold<br>temperature,<br>End with high<br>temperature,<br>IEC60068-2-14:1984,G<br>B2423.22-2002 |

| 7  | Electro Static<br>Discharge<br>(operation)     | C=150pF R=330Ω Air: ±8KV Contact:±4KV 5point/panel, 5times  | IEC61000-4-2:2001<br>GB/T17626.2-2006                                                                     |

Note1: Ts is the temperature of panel's surface.

Note2: Ta is the ambient temperature of sample.

Note3: Before cosmetic and function test, the product must have enough recovery time, at least 2 hours at room temperature.

Note 4: In the standard condition, there shall be no practical problem that may affect the display function. After the reliability test, the product only guarantees operation, but don't guarantee all of the cosmetic specification.

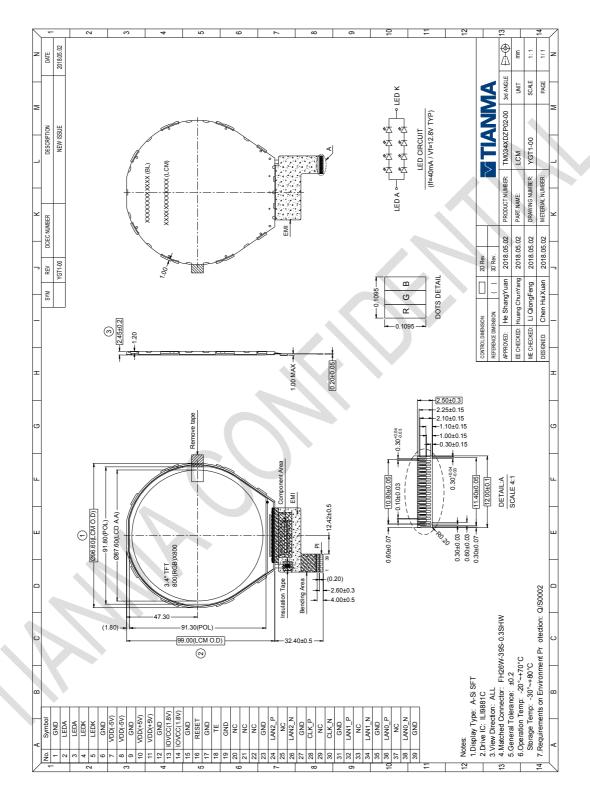

# 8 Mechanical Drawing

## 8.1 LCM Drawing

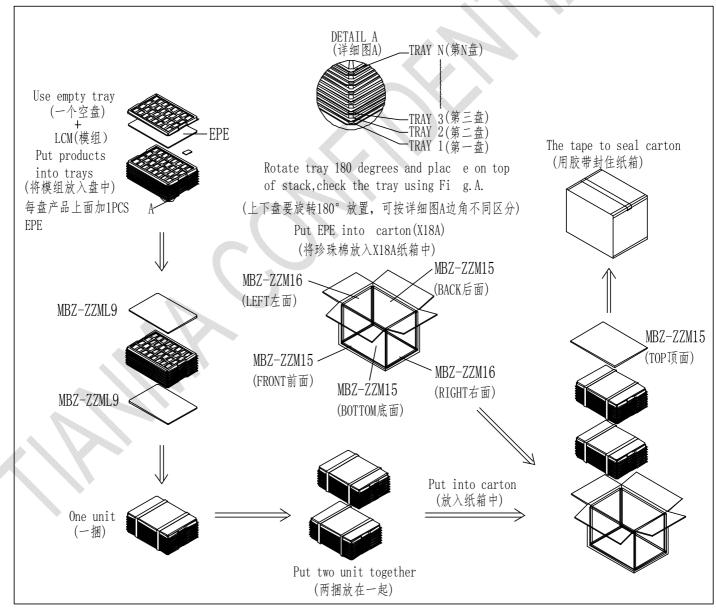

# 9 Packing Drawing

### 9.1 Per Carton

| No | Item         | Model (Materiel)       | Dimensions(mm) | Unit Weight(Kg) | Quantity | Remark      |

|----|--------------|------------------------|----------------|-----------------|----------|-------------|

| 1  | LCM module   | TM034XDZP02-00         | 96.6×99.0×2.45 | TBD             | 112      |             |

| 2  | Tray         | TM034XDZP02-00 YBZ1-00 | 356x256x12     | TBD             | 30       |             |

| 3  | EPE (珍珠棉1)   | TM034XVZP01-00 YPF1-00 | 312.67×216×1   | TBD             | 28       |             |

| 4  | EPE (珍珠棉2)   | MBZ-ZZML9              | 336×246×8      | TBD             | 4        |             |

| 5  | EPE(珍珠棉3)    | MBZ-ZZM15              | 375×275×10     | TBD             | 4        | <b>&gt;</b> |

| 6  | EPE(珍珠棉4)    | MBZ-ZZM16              | 250×280×12     | TBD             | 2        |             |

| 7  | Carton(纸箱)   | X18A                   | 395×290×315    | TBD             | 1        |             |

| 8  | Total weight | TBD                    |                |                 |          |             |

### 9.2 Packaging Specification and Quantity

- (1) LCM quantity per tray (每盘模组数量):4 pcs

- (2) Total LCM quantity per group(每组模组总数量): 56 pcs(14Tray盘+1 Enpty tray空盘)

- (3) Total LCM quantity per Carton(每箱模组总数量): quantity per group(每组模组总数量)56 pcs×group quantity per Carton(每箱组数量)2= 112 pcs

### 9.3 LCM 喷码规格

| 喷码位置 | 背光源背面                             |  |

|------|-----------------------------------|--|

| 喷码内容 | 5一行: 厂别 模块型号 生产日期<br>5二行: 投产单号 班别 |  |

|      | 生产日期格式为年月日 (YYMMDD)               |  |

### 9.4 Packing Form

#### 10 Precautions for Use of LCD Modules

- 10.1 Handling Precautions

- 10.1.1 The display panel is made of glass. Do not subject it to a mechanical shock by dropping it from a high place, etc.

- 10.1.2 If the display panel is damaged and the liquid crystal substance inside it leaks out, be sure not to get any in your mouth, if the substance comes into contact with your skin or clothes, promptly wash it off using soap and water.

- 10.1.3 Do not apply excessive force to the display surface or the adjoining areas since this may cause the color tone to vary.

- 10.1.4 The polarizer covering the display surface of the LCD module is soft and easily scratched. Handle this polarizer carefully.

- 10.1.5 If the display surface is contaMinated, breathe on the surface and gently wipe it with a soft dry cloth. If still not completely clear, moisten cloth with one of the following solvents:

- Isopropyl alcohol

- Ethyl alcohol

Solvents other than those mentioned above may damage the polarizer. Especially, do not use the following:

- Water

- Ketone

- Aromatic solvents

- 10.1.6 Do not attempt to disassemble the LCD Module.

- 10.1.7 If the logic circuit power is off, do not apply the input signals.

- 10.1.8 To prevent destruction of the elements by static electricity, be careful to maintain an optimum work environment.

- 13.1.8.1 Be sure to ground the body when handling the LCD Modules.

- 13.1.8.2 Tools required for assembly, such as soldering irons, must be properly ground.

- 13.1.8.3 To reduce the amount of static electricity generated, do not conduct assembly and other work under dry conditions.

- 3.1.8.4 The LCD Module is coated with a film to protect the display surface. Be care when peeling off this protective film since static electricity may be generated.

- 10.2 Storage precautions

- 10.2.1 When storing the LCD modules, avoid exposure to direct sunlight or to the light of fluorescent lamps.

- 10.2.2 The LCD modules should be stored under the storage temperature range. If the LCD modules will be stored for a long time, the recommend condition is:

- Temperature :  $0^{\circ}$ C  $\sim 40^{\circ}$ C Relatively humidity:  $\leq 80\%$

- 10.2.3 The LCD modules should be stored in the room without acid, alkali and harmful gas.

- 10.3 Transportation Precautions

#### Model No. TM034XDZP02-00

- 10.3.1 The LCD modules should be no falling and violent shocking during transportation, and also should avoid excessive press, water, damp and sunshine.

- 10.3.2 About the limited warranty unless special agreement between TIANMA and customer TIANMA will replace or repair any of its products that are found to be functionally defective when inspected in accordance with TIANMA acceptance standards for a period of one yearfrom data of shipments. 除天马跟客户签定协议外,对确认为属于产品本身功能性缺陷的,在天马可接受范围内可进行退换或维修,天马保质期为从出货日期起一年内有效。